问题描述

还在为 K230/K230D 原理图 PCB 设计的细节疏漏发愁?担心电源时序、信号完整性踩坑?现在不用慌! Kendryte 原厂重磅推出 [K230/K230D原理图PCB设计CHECKLIST] ,从核心电路到外设接口,从原理图规范到 PCB 布局,一站式覆盖硬件设计全流程,帮你把“本地自查”做到位,大幅降低后期调试风险!

这份 CHECKLIST 有多实用?原厂硬件工程师手把手划重点——

✅ 电源地设计不踩雷:明确 SOC 和外设的 IO 电压匹配要求(1.8V/3.3V需电平适配),严格规定上电顺序(VDD0P8_CORE先于VDD1P8等上电), 明确未使用模块的供电要求,即使未用ADC/CODEC 也需给 AVDD1P8_ADC/CODEC 供电,磁珠隔离+滤波网络配置细节直接给到位!

✅ 关键电路全覆盖:主晶振24MHz±20ppm偏差要求、DDR 设计“抄作业”参考(建议对齐“庐山派”开发板)、PMU持续供电要点、MIPI RX/TX差分信号“间隔插 GND 管脚”规则,每个环节都有明确标准!

✅ 外设接口无死角:USB2.0 需 ESD 保护(寄生电容<1pF)、EMMC信号上拉/下拉电阻范围(10K-100K)、模拟音频 MICBIAS 电容摆放(4.7μF+100nF对地),甚至 TF 卡/ FLASH 线长偏差(±50mil内)都标注清晰!

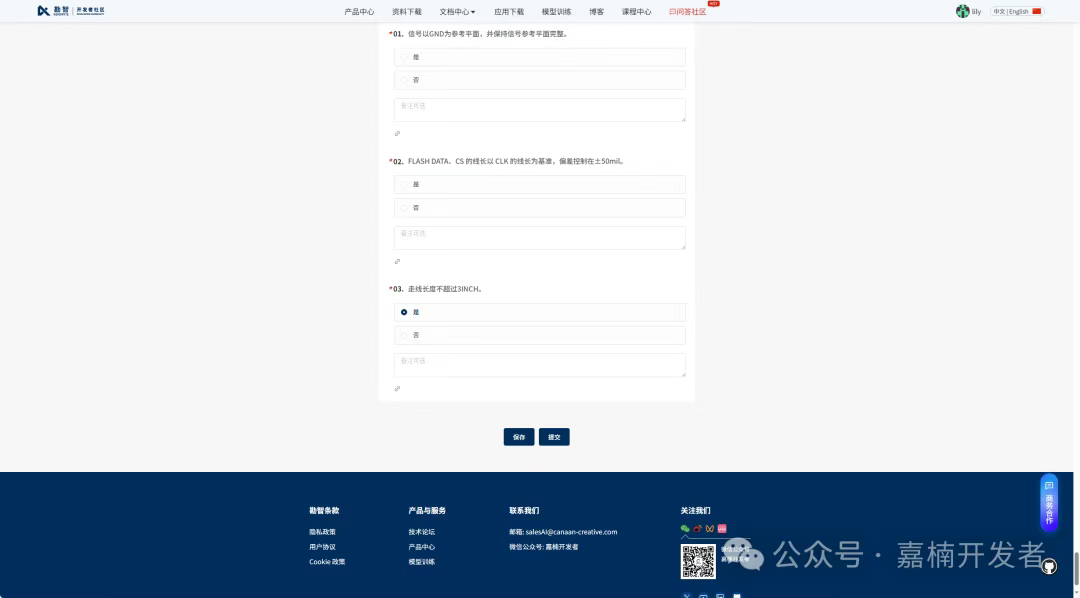

✅ 原厂硬件工程师协助:点击【保存】和 【提交】之后,CheckList 和附件会发送到原厂硬件工程师邮箱,协助你 check 原理图和 PCB 设计!

不管你是刚接触 K230/K230D 的硬件新人,还是需要规范流程的资深工程师,这份 CHECKLIST 都是“避坑神器”——不用等外部审核,本地就能对照检查:电源域是否全供电?晶体走线有没有包地?MIPI 差分阻抗是否达标?每一项都有明确判定标准,让设计合规性“肉眼可见”!

👉 立即戳链接获取:https://www.kendryte.com/zh/tools/pcb_checklist 有了原厂这份“设计说明书”,K230硬件开发效率直接拉满,快转给身边做K230项目的小伙伴,一起把设计风险扼杀在源头!